IMPERIAL COLLEGE LONDON

DEPARTMENT OF COMPUTING

## The Acceleration of multi-factor Merton model on FPGA

*Author:* Pengyu Guo Supervisor: Luk Wayne

Submitted in partial fulfillment of the requirements for the MSc degree in MSc of Imperial College London

September 2020

#### Abstract

Credit risk stands for the risk of losses caused by unwanted events, such as the default of an obligor. The managing of portfolio credit risks is crucial for financial institutions. The multi-factor Merton model is one of the most widely used tools that modelling the credit risks for financial institutions. Typically, the implementation of the multi-factor Merton model involves Monte Carlo simulations which are time-consuming. This would significantly restrict its usability in daily credit risk measurement. In this report, we propose an FPGA architecture for credit-risk measurements in the multi-factor Merton models. The presented architecture uses a variety of optimisation techniques such as kernel vectorisation and loop unrolling, to optimise the performance of the FPGA implementation. The evaluation results show that compare to a basic C++ implementation running on a single core Intel i5-4210 CPU, our proposed FPGA implementation can achieve an acceleration of up to 22 times, with a precision loss of less than  $10^{-8}$ .

## Acknowledgments

I am extremely thankful for Prof Wayne Luk, for his academic guidance throughout the project. I am also extremely grateful to Dr Ce Guo, for his technical assistance, and also for the huge amount of confidence he placed in me to help me finish this project.

I would be also grateful to Prof Stephen Weston, for his devotion to his knowledge of the multi-factor Merton models.

I would also like to express my sincere thanks to my supportive parents, who give me this great opportunity to study at Imperial college London and for always being there for me.

# Contents

| 1 | Intr             | oductio                      | n                                     | 1  |  |

|---|------------------|------------------------------|---------------------------------------|----|--|

| 2 | Bac              | kgroun                       | d and related work                    | 4  |  |

|   | 2.1 Background   |                              |                                       |    |  |

|   | 2.2 Related work |                              |                                       |    |  |

|   | 2.3              | Multi-                       | factor Merton model                   | 6  |  |

|   |                  | 2.3.1                        | Model structure                       | 6  |  |

|   |                  | 2.3.2                        | Monte Carlo Simulation                | 8  |  |

|   | 2.4              | Intel F                      | FPGA SDK for OpenCL                   | 9  |  |

|   |                  | 2.4.1                        | OpenCL SDK programming model          | 9  |  |

|   |                  | 2.4.2                        | Memory structures                     | 13 |  |

| 3 | FPG              | A desig                      | gn and implementation                 | 15 |  |

|   | 3.1              | 3.1 Basic C++ implementation |                                       | 15 |  |

|   | 3.2              | NDRa                         | nge Mode                              | 18 |  |

|   |                  | 3.2.1                        | Basic Implementation                  | 19 |  |

|   |                  | 3.2.2                        | Kernel vectorization implementation   | 21 |  |

|   |                  | 3.2.3                        | Multiple compute units implementation | 25 |  |

|   |                  | 3.2.4                        | Loop unrolling implementation         | 27 |  |

|   | 3.3              | Single                       | work-item                             | 30 |  |

|   |                  | 3.3.1                        | Single work-item basic implementation | 31 |  |

|   |                  | 3.3.2                        | Loop unrolling implementation         | 35 |  |

|   | 3.4              | Fixed                        | point vs Floating point               | 37 |  |

|   | 3.5              | Optim                        | ised implementation                   | 38 |  |

| 4 | Eval             | luation                      |                                       | 42 |  |

|   | 4.1              | Accura                       | acy evaluation                        | 42 |  |

|   |                  | 4.1.1                        | Result distribution analysis          | 43 |  |

|    |                                       | 4.1.2                      | Result accuracy analysis                                                  | 44 |

|----|---------------------------------------|----------------------------|---------------------------------------------------------------------------|----|

|    | 4.2                                   | Perfor                     | mance Comparison Between CPU and FPGA Implementations .                   | 46 |

|    | 4.3                                   | Result                     | analyze                                                                   | 48 |

|    |                                       | 4.3.1                      | Compare with Intel FPGA implementation of single factor Mer-<br>ton model | 49 |

|    |                                       | 4.3.2                      | Compare with CUDA GPU implementation of multi-factor Mer-<br>ton model    | 50 |

|    |                                       | 4.3.3                      | Compare with an outstanding GPU implementation of the multi-              |    |

|    |                                       |                            | factor Merton model                                                       | 51 |

| 5  | Con                                   | Conclusion and future work |                                                                           | 52 |

| Aŗ | pend                                  | lices                      |                                                                           |    |

| Α  | A Legal and Ethical Considerations 56 |                            |                                                                           |    |

# Chapter 1

# Introduction

Credit risk analysis and management have become one of the most important topics within a plethora of financial and lending institutions in recent years. Credit risk represents the risk of losses arising from some unexpected credit incidents such as the default of a counterparty, which often leads to incidents which have unwanted negative effects. When modelling credit risks, the key difficulties arise from the fact that default incidents are very unusual and that they always happen suddenly. However, when such incident occurs, it often leads to huge losses and disrupts the normal operations of financial institutions.

Concentration risks are referred to as a special type of credit risks, defined as the potential loss occurs from disproportionate loan distribution to single borrowers or regional sectors

Historical experience has already shown that the concentration risk in asset portfolios is one of the main reasons of bank distress. Furthermore, the huge amount of regulations imposed by supervisory authorities to regulate the concentration risks also illustrates the importance of diversifying loan portfolios for both nations and industries. Therefore, the measurement of potential concentration risks within a portfolio is very important.

In general, existing methods for measuring the concentration risks can be roughly divided into two groups [1]. The first group consists of asset-value models, in which the default of a corporation is modelled by the relationship between its assets and its liabilities at the end of a given period. Default risk in models of this type relies heav-

ily on asset value's stochastic evolution, and default happens when the value of the variable that describes the asset value decreases below a specific value representing the liabilities threshold.

The second category is reduced-form models, which do not model the relationship between firm liabilities and firm asset value as what asset-value models did. In contrast, it models the process of defaults directly, instead of conducting a random evolution asset value process and model the default of a firm indirectly. In this type of models, a firm's probability of default is typically modeled as a distribution that depends on some economic covariables. However, compared to asset-value models, the reduced-form models are proved [2][3] to be a poor match for the observed real-world levels. Therefore, we select the asset-value models as the prototype of the concentration risk measurement method used in this work. Specifically, our study focuses mainly on one of the most famous and widely-used asset-value model - the multi-factor Merton model.

There are varieties of asset-Value models have already been developed by some prior researches, such as the KMV model[4] and the CreditMetrics model[5], both software-based and running on general CPUs. Therefore, these tools are typically serially-executed and lack parallel computing. This is especially troublesome in situations where the asset value process needs to be simulated for many scenarios. Because by doing so, it typically produces a high computational complexity due to the large dimensionality of counterparty information and therefore is time-consuming. Therefore, a high-performance implementation that focus on optimizing the execution speed of these models is needed to be developed to leverage the capabilities of asset-value models completely. Field Programmable Gate Array (FPGA)-based hardware methods has shown promising performance in terms of energy saving, and increasing the computing speed of the asset-value models [6].

To conclude, the aim of this project is to address the major challenge in concentration risk measurement: the time-consuming problem. The description of how we address such challenge is presented in Section 3. The evaluation of how well this challenge is met by our method is presented in Section 4.

Overall, in order to address the above challenge, this work proposes an FPGA-based

acceleration approach to speed up the execution of the multi-factor Merton model so that the potential concentration risks of a portfolio can be measured more quickly.

To the best of the authors' knowledge, this is the first work that proposes FPGA implementation for the multi-factor Merton model. The purpose of this study is to make up the gap in this area and to develop an FPGA-based accelerator with high accuracy and fast processing speed.

The main contributions of this work are summarised as follows:

- We present a comprehensive set of basic manual optimisation methods for Intel FPGA SDK for OpenCL and discuss how each of them affects the performance of our FPGA implementation. By doing so, we hope to provide some insights to researchers who have similar studies as ours (Section 3.1 3.3);

- We quantitatively analysed the impact of using fixed-point and floating-point representation on the speed and accuracy of our FPGA implementation. In addition, we have also pointed out how to further improve the running speed of an FPGA implementation when a fixed-point representation is used (Section 3.4);

- We proposed an FPGA-based accelerator for the multi-factor Merton model to speed up the model execution. We show that compared to a basic C++ implementation running on a single core Intel i5-4210 CPU, the proposed FPGA implementation can achieve an acceleration of up to 22 times, with a precision loss of less than 10<sup>-8</sup> (Section 3.5);

- We conducted a series of comprehensive evaluations on the accuracy and speed of our FPGA implementation. Besides, we have also compared our implementation with some previous similar designs. By doing so, we have identified some of the shortcomings of our implementation, and presented how can we improve our implementation in future work (Section 4);

# **Chapter 2**

# **Background and related work**

## 2.1 Background

Maintaining the stability of central counterparties(CCP) has become increasingly important in recent years due to the significant increase in central clearing. Among them, the management and modelling of the concentration risks are a core concern within the risk management processes at central counterparties as these risks can become systemic if a CCP is large enough. The concentration risk can be defined as the potential loss during the running of the CCP, because of an insufficient diversification of the CCP's collateral pool.

Recently, asset-value models obtained positive success in measuring the concentration risks. This type of models uses a geometric Brownian motion to simulate an obligor's asset value process. The default of the obligor in the model happens when its asset value at maturity time is lower than its liabilities.

The multi-factor Merton model [7] is one of the most popular asset-value models for concentration risk measurement. The multi-factor Merton model tries to interpret the asset of an obligor in terms of some potential economic variables so that these economic factors can explain some large portfolio losses. Besides, factor models' computational effort can be easily regulated by the number of economic variables included in the model. Being one of the asset-value models, in multi-factor Merton model, an obligor's default or survival is also made by comparing the obligor's asset value at maturity time to a certain default threshold.

Being one of the asset-value models, the multi-factor Merton model leads to a reliable risk analysis result. However, as mentioned in Section one, this kind of models are typically computationally intensive, which usually requires massive quantities of computational resources. Fortunately, these types of models usually have parallelism in many computational blocks and therefore it has a basis for parallelization by some hardware frameworks like FPGAs.

## 2.2 Related work

There is plenty of literature accelerating the multi-factor Merton model. Béresand and Bris [8] proposed a novel approach to speed up the execution of the multi-factor Merton model using importance sampling and GPUs. The accelerator uses a Gaussian mixture model to conduct importance sampling, and therefore avoid conducting time-consuming Monte Carlo simulations. They have found that the model run on an NVIDIA Kepler K20 accelerator is faster than run on the Intel Sandy Bridge E5-2470 CPU for a factor of 19 to 287, depending on the structure of the portfolio.

In a similar study, Zhang and Oosterlee [9] has proved that when the CPUs and GPUs are used concurrently to accelerate the model operation, different workloads partitions between CPU and GPU will affect the final acceleration effect. They have shown for European options that the highest speedup can be achieved if most of the basic mathematical operations, such as big metric multiplications, are performed directly on the GPU. By doing so, the bottleneck of limited bandwidth between CPU and GPU can be greatly avoided.

Besides, FPGAs based hardware acceleration is also often used to improve the running speed of asset-value models. Being one of the research group acting on FPGA accelerators, Tian and Benkrid [10] .implemented an FPGA-based option pricing accelerator on an asset-value model and achieves a speedup of 340 times over a software implementation running on an Intel Pentium IV CPU. Their later work that take use of Quasi Monte Carlo pricing strategy achieves 10 times speedup over an NVIDIA 8800GTX GPU and 500 times speedup over an Intel Xeon CPU[11].

A study given by Delivorias[12] also gives a similar result. They compared the acceleration effect of the Heston model simulation on both GPU and FPGA clusters. The

Heston model is also one of the typical asset-value models. The experiment result shows that: the FPGA version of the model run on Maxeler is 1.75 times faster than the GPU accelerator with 2x Tesla M2090.

In view of all that has been discussed above, it was finally decided to build an FPGA hardware design of the multi-factor Merton model in this project. The reasons why FPGAs is preferred over CPU and GPU are as follows. First of all, FPGAs presents a hardware implementation of the original algorithm whereas CPUs and GPUs accelerators are generally software-based. Due to its natural, the hardware is always faster than software. Furthermore, it has already been proved that using FPGA consumes less energy. A study given by Schryver et al. [13] shows that when doing a single-level Monte-Carlo simulation, a Tesla C2050 GPU achieves a 5.5x speedup by consuming 30% of the total energy. Whereas a Virtex-5 FPGA achieved the same throughput by only consuming 4% of the total energy.

## 2.3 Multi-factor Merton model

#### 2.3.1 Model structure

As mentioned before, the multi-factor Merton model is used in this project to measure the concentration risk in credit portfolios. This section mainly introduces the structure of this model.

Consider a portfolio of N risky borrowers. Let  $V_t^{(n)}$  to be the asset value of borrower n at time t (before the maturity time). Each borrower has a default threshold such that borrower n defaults if  $V_t^{(n)}$  lowers than this threshold at maturity time. Therefore, in this model,  $V_t^{(n)}$  can be regarded as a latent variable that driving the event of default.

Let  $r_n$  to be the  $n_{th}$  borrower's asset-value log returns, where T stands for the maturity time.

$$r_n = \log(V_T^n / V_0^n) \tag{2.1}$$

$r_n$  is assumed to depend linearly on K systematic risk factors  $(X_1, X_2, ..., X_K)$  as well as on an idiosyncratic term  $\epsilon_n$ . Both the systematic risk factors and the idiosyncratic term are standard normally distributed. In addition,  $\epsilon_n$  is independent from the systematic risk factors  $X_K$ . Then, the asset value log-returns  $r_n$  can be rewrote in the following form:

$$r_n = \beta_n * Y_n + \sqrt{1 - \beta_n^2} * \epsilon_n \tag{2.2}$$

$Y_n$  denotes the borrower's composite factor,  $\beta_n$  measures the correlation between  $r_n$  and  $Y_n$ ,  $\epsilon_n$  denotes the idiosyncratic term.

Therefore,  $Y_n$  can be disintegrated into the K independent systematic factors we mentioned above:

$$Y_n = \sum_{k=1}^{K} \alpha_{n,k} * X_k \tag{2.3}$$

Where  $X_k$  represents the systematic risk factors  $(X_1, X_2, ..., X_K)$  and  $\alpha_{n,k}$  explains borrower *n*'s dependence on a systematic factor  $X_k$ .

Since the composite risk factor  $Y_n$  and the idiosyncratic term  $\epsilon_n$  are assumed to be independent, we can derive the following equation from (2.2):

$$V(r_n) = \beta_n^2 * V(Y_n) + (1 - \beta_n^2) * V(\epsilon_n)$$

(2.4)

Then  $\beta_n^2 * V(Y_n)$  captures borrower n's systematic risk, and  $(1 - \beta_n^2) * V(\epsilon_n)$  stands for the idiosyncratic term, which measures the other risk factors that cannot be explained by the systematic factors.

It is worth noting that, since  $X_k, r_n$  and  $\epsilon_n$  are assumed to be standard normally distributed, then in order to make  $V(Y_n) = 1$ , the coefficient  $\alpha_{n,k}$  in equation (2.3) must verify:  $\sum_{k=1}^{K} \alpha_{n,k}^2 = 1$

With previous knowledge we can now measure the concentration risks of a portfolio. Let  $PD_n$  to be the one year default probability of borrower n:  $PD_n = P(r_n < c_n)$ . Since  $r_n$  are assumed to be standard normally distributed,  $c_n$  can be rewrite as:

$$c_n = \phi^{-1}(PD_n) \tag{2.5}$$

where  $\phi$  is the cumulative distribution function.

If we plug equation (2.2) and (2.5) to the default condition  $r_n < c_n$ , we can obtain:

$$\phi_n < \frac{\phi^{-1}(PD_n) - \beta_n Y_n}{\sqrt{1 - \beta_n^2}} \tag{2.6}$$

Thus, to conclude, the default probability of borrower n that conditional on the composite factor  $Y_n$ , is given by:

$$PD_{n}(Y_{n}) = \phi(\frac{\phi^{-1}(PD_{n}) - \beta_{n}Y_{n}}{\sqrt{1 - \beta_{n}^{2}}})$$

(2.7)

Then, the portfolio loss variable L, which measures the quality of the current credit portfolio, can be defined as follow.

$$L = \sum_{n=1}^{N} s_n * LGD_n * 1\{r_n < \phi^{-1}(PD_n)\}$$

(2.8)

Where  $s_n$  is the exposure share of borrower n:  $s_n = \frac{EAD_n}{\sum_{n=1}^{N} EAD_n}$ .  $EAD_n$  is the exposure of each borrower's loan.  $LGD_n$  determines the amount of loss when borrower n default. It is assumed that LGD are independent for different borrowers and for all other variables in the model. And 1{.} here denotes the indicator function.

#### 2.3.2 Monte Carlo Simulation

Using equation (2.8), we can calculate the loss rate of a certain credit portfolio according to the given systematic risk factors. However, in order to more comprehensively assess the quality of this credit portfolio and detect the potential risks within it, we need to obtain the loss distribution of this credit portfolio. This can be done by conducting a Monte Carlo simulation based on different systematic risk factors.

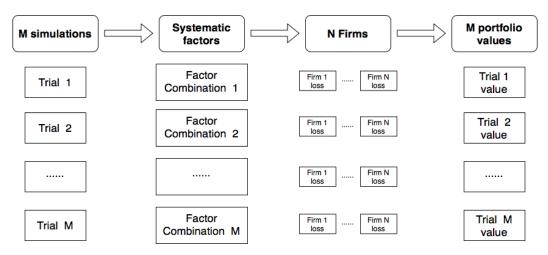

Figure 2.1: figure shows the procedure of the Monte Carlo Simulation

As shown in Figure 2.1, the Monte Carlo simulation involves M trials. A random set of systematic factors is generated in each trial, which is then used by firms to conduct the asset value process and decide whether the firm is default or not. Then, the portfolio loss value of each trial is calculated as:

$$L^{i} = \sum_{n=1}^{N} s_{n} * LGD_{n}^{i} * 1\{r_{n} < \phi^{-1}(PD_{n})\}^{i}$$

(2.9)

The upper index *i* indicates the index of a particular Monte Carlo sample. It is worth noting that, we assume that portfolios are infinitely fine-grained so that the idiosyncratic risk term can be fully removed from the calculation.

Having the distribution of portfolio losses, the quality of a certain portfolio can then be measured using a metric called "value at risk (VaR)", which is often used by firms of the financial institutions to measure the risk of loss for investments. In our work, VaR is defined as the p quantile of  $L = (L^1, L^2, ..., L^M)$ .

Therefore, the M-trial Monte Carlo simulation approximates the value at risk of a certain portfolio as:

$$VaR(L) = min\{L^{i}: \psi(L^{i}) \le (1-p) * M\}$$

=  $L^{[[Mp]]}$  (2.10)

Where  $\psi(L^i) = \sum_{j=1}^M (L^j > L^i)$  and  $L^{[[x]]}$  is the x - th loss in the ascendant sorted loss sequence L.

## 2.4 Intel FPGA SDK for OpenCL

This work uses Intel FPGA SDK for OpenCL to develop the FPGA implementation of the multi-factor Merton model. To make things easier for the reader to understand, before discussing the structure of our FPGA Accelerator, the internal structure of the Intel FPGA SDK for OpenCL, as well as its memory structure, is first introduced in this section.

#### 2.4.1 OpenCL SDK programming model

In this section, we discuss how OpenCL programs are executed. OpenCL programs consist of one or more kernels, and each kernel represents a function of the OpenCL

program code. The OpenCL SDK provides two different types of kernel: the NDRange kernel and the Single work-item kernel.

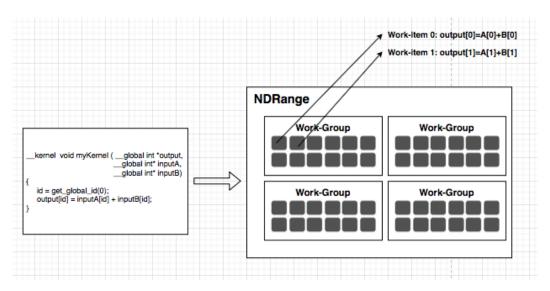

Consider a kernel that calculates the addition of two N-element Vectors. If the kernel is executed in NDRange mode, an index space is generated accordingly as shown in Figure 2.2.

Figure 2.2: NDRange kernel index space

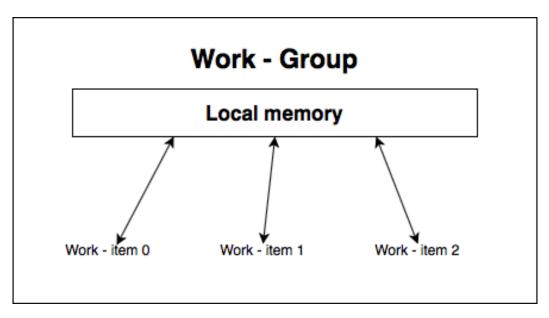

Each point of this space represents a single work-item, and each work-item is responsible for executing the same piece of kernel code. In our example, each workitem is in charge of handling the addition of two elements. Besides, an unique ID called global ID is assigned to each work-item, such that different sets of data can be mapped to different work-items according to this global ID. Each work-group consists of a collection of work-items, and a collection of work-group forms an NDRange kernel. One of the biggest benefits of this design is that the work-items within the same work-group can share data through a fast on-chip local memory. Thus, there is no need to extract the same piece of data repeatedly while running different work items.

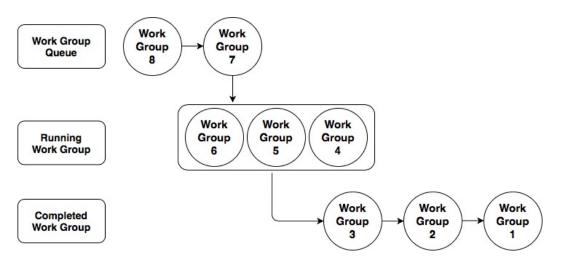

Imagine N = 128, that is, we are trying to add two vectors with length 128. Then there will be 128 work-items in total, each responsible for adding two single elements. Assume that the 128 work-items are divided into 8 work-groups, each consists of 16 work-items, and there are three available compute units. Then an NDRange kernel will execute as follow:

Figure 2.3: The execution of NDRange kernels

Since there are three compute units available, each time three work-groups are allowed to be processed in parallel. Moreover, the compiler also performs work-group level pipelining automatically. By doing so, it enables several work-groups to be executed concurrently in the same compute unit and the efficiency of all pipelines in the compute unit can hence be optimised.

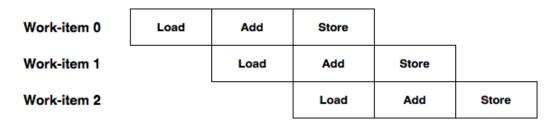

Figure 2.4: The execution of Single work-item kernels

The single work-item kernel works in a slightly different way - it has a single workgroup that contains only one work-item. As shown in Figure 2.4, the offline compiler of OpenCL take use of a pipeline structure to speed up the computation for each kernel. A new work-item is inserted into the pipeline at each clock cycle, so that several work-items can be executed in parallel. By doing so, compare with replicating hardware for each work-item, the pipeline structure is more effective in terms of hardware resources as all work-items are executed in the same pipeline. Besides, the pipeline can make the memory bandwidth more efficient, as the input data of each work-item is loaded sequentially at each clock cycle. Since FPGAs' maximum external memory bandwidths are lower than that of GPUs, the pipeline technique is very important for FPGAs.

In addition to the different run time logic, another major difference between the two different kinds of kernel is the way they share data. The sharing of data between work-items in NDRange kernels is done by using a shared local memory as seen in Figure 2.5. Whereas single work-item kernels share data via a specific feedbacks channel as shown in Figure 2.6. This single work-item kernel's special technique of sharing data is a key factor in its ability to handle data dependencies between work items.

Figure 2.5: NDRange kernel's memory sharing strategy

Figure 2.6: Single work-item kernel's memory sharing strategy

### 2.4.2 Memory structures

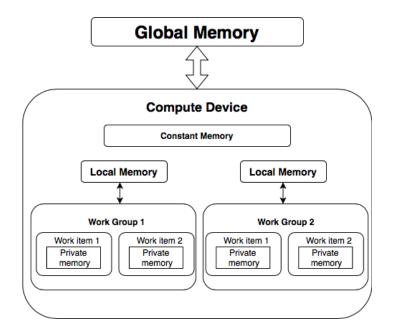

The OpenCL SDK supports four different memory types: private memory, local memory, global memory and constant memory, as shown in Figure 2.7.

Figure 2.7: Memory structure of the Intel FPGA SDK for OpenCL

Global memory: The global memory is off-chip memory and has a large capacity. Although global memory storage has the highest access latency amongst the four memory types, it can still be very efficient. This is because the global memory bandwidth can be optimised by utilising LSU embedded caches which can provide coalescent memory access. Therefore, if there are repetitive and low-frequency global cache accesses, data is best to be stored in LSU caches. Compared with using global memory directly, a shorter access latency and a higher memory bandwidth can be achieved.

Constant memory: Constant memory locates in global memory, and therefore it is accessible to all work-groups. However, the compiler always loads it into a fast onchip read-only cache at runtime. Therefore, by its nature, the access latency of the constant memory is much lower than that of the global memory. Thus, The constant memory is often used for data storage that require high-bandwidth memory access and is constant across several invocations of a kernel.

Local and private memory: Typically, due to the use of a small-size but high-performance

local cache, local and private memory's access latency and memory bandwidth is far more better than that of the global memory. The major difference between private memory and local memory is their accessibility for different work-items. The local memory is visible to all work-items within the same work-group, whereas private variables are stored in private registers, and are accessible only to the work-item that own this private register.

## **Chapter 3**

# **FPGA design and implementation**

This chapter describes the implementation of our multi-factor Merton model in FPGA. In our work, we tried to use both NDRange mode and single work-item mode to implement our model and apply various methods to both modes to improve their performance. It is worth indicating that there is only one kernel function for each of the two implementations. Although distributing the model operation process to multiple kernels can significantly reduce the programming difficulty, the communication between different kernels has transmission consumption, which will affect the running speed. Therefore, we only keep one kernel function and let this kernel reproduce the asset value process of the multi-factor Merton model as we discussed in Section 2.3.1.

### **3.1** Basic C++ implementation

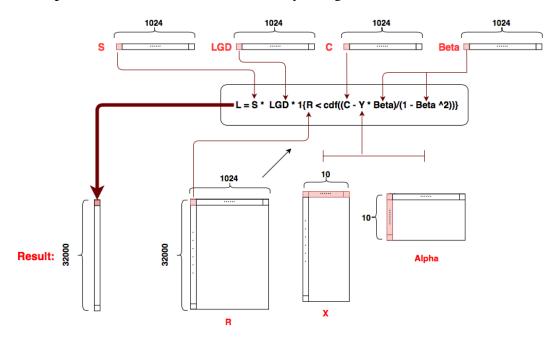

This section describes how ordinary C++ code reproduced the Monte Carlo Simulation of the multi-factor Merton model. First of all, suppose we have 1024 obligors and we need 32000 Monte Carlo simulation to measure the quality of a certain credit portfolio, and there are 10 systematic factors affecting each firm's asset value process. Then the input and output of the program will be as shown in Table 3.1:

| Туре   | Variable name | Dimension    | Description                      | Variables in the model         |  |

|--------|---------------|--------------|----------------------------------|--------------------------------|--|

|        | S             | 1 * 1024     | The exposure share of each       | $s_n$ in equation 2.8          |  |

|        |               | 1 1024       | obligor                          |                                |  |

|        | LGD           | 1 * 1024     | The loss given default of        | $LGD_n$ in equation 2.8        |  |

| Input  |               |              | each obligor                     |                                |  |

| input  | R             | 32000 * 1024 | The asset-value log returns      | $r_n$ in equation 2.8          |  |

|        |               |              | of each obligor in each scenario |                                |  |

|        | С             | 1 * 1024     | The default threshold of         | $c_n$ in equation 2.5          |  |

|        | 0             |              | each obligor                     |                                |  |

|        | Beta          | 1 * 1024     | The correlation between the      | $\beta_n$ in equation 2.2      |  |

|        |               |              | asset-value of each obligor      |                                |  |

|        | Deta          |              | and its corresponding            |                                |  |

|        |               |              | composite factors                |                                |  |

|        | х             | 32000 * 10   | Systematic factors for           | $\alpha_{n,k}$ in equation 2.3 |  |

|        |               |              | each scenario                    |                                |  |

|        | Alpha         | 10 * 1024    | Each obligor's dependence        | $X_K$ in equation 2.3          |  |

|        | rupitu        |              | on each systematic factors       |                                |  |

|        |               |              | The portfolio loss of            |                                |  |

| Output | Result        | 32000 * 1    | each Monte Carlo                 | <i>L</i> in equation 2.8       |  |

|        |               |              | simulation scenario              |                                |  |

### Table 3.1: Data specification

In short, the basic C++ implementation performs the following:

#### Algorithm 1 Multi Factor Merton Model Monte Carlo Simulation

```

1: for i = 1 to numOfScenario do

portfolioLoss = 0.0

2:

for j = 1 to numOfOblg do

3:

Extract the S_j, LGD_j, C_j, \beta_j, \alpha_j from the input data.

4:

Compute the composite risk factor: Y_j = \sum_{k=1}^{K} \alpha_{n,k} X_k

5:

ncdf = cdf((C_j - Y_j * \beta_j) / (sqrt(1 - \beta_j^2)))

6:

portfolioLoss + = S_j * LGD_j * (U_{i,j} < ncdf)

7:

8:

end for

Result[i] = portfolioLoss

9:

10: end for

```

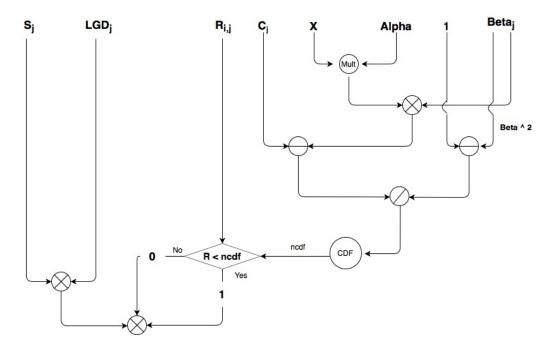

The outer loop is responsible for conducting Monte Carlo simulation and recording the portfolio loss of each simulation. The inner loop iterate through each obligor and calculates their composite risk factors, then use this composite risk factor to conduct the evolution of their asset-value, and finally decide whether this obligor default or nor. This process can be described intuitively using the flow chart below.

Figure 3.1: The computational spatial layout of the model

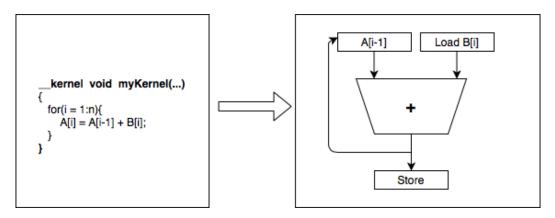

Moreover, as mentioned before, two different types of kernel are used to implement the FPGA version of the multi-factor Merton model. The main difference between them is the different data sharing strategy and the different division of workgroups/work-items. Since they have the same internal kernel logic, they can share the same set of hardware structure as presented in Figure 3.2.

Figure 3.2: The hardware logic of both types of kernel

## 3.2 NDRange Mode

This section discusses our NDRange implementation of the multi-factor Merton model. The NDRange mode mainly benefits from the parallelization of individual work items. Therefore, programmers usually need to specify the thread-level parallelism mechanism explicitly. The following subsections present several different optimisation techniques under NDRange mode. These optimisation methods are evaluated separately in each subsection to analyse how each of them affects the performance of our implementation. The optimal combination of these optimisation techniques under NDRange mode is provided in Section 3.5. Besides, at the end of each subsection, an Arria 10 FPGA board was used to evaluate the performance of each optimisation technique, with a resource report attached. The execution time of the corresponding FPGA implementation was also compared to that of running on a single-core Intel Core i5-4210 CPU. A more comprehensive comparison is provided in Chapter 4 (i.e. compare the speedup effect of our FPGA implementation to the software implementation running on a 1/2/4/8 cores CPU).

### 3.2.1 Basic Implementation

This implementation is the normal NDRange mode kernel function of the multifactor Merton model Monte Carlo Simulation with the references from the C++ implementation given in Algorithm 1. The NDRange kernel generates a deeply pipelined version of the kernel each time so that it can take advantage of the pipelining parallelism mechanism. Therefore, the outer *for* loop in Algorithm 1 is removed so that the C++ implementation can be parallelized. As shown in Algorithm 2, to index the specific work-item executed by the host, the OpenCL function *get\_global\_id()* is used to determine the index of the Monte Carlo simulation for the kernel function. The rest of the code is identical to the C++ implementation.

Algorithm 2 multi-factor Merton model - NDRange Mode basic implementation

- 1:  $\mathbf{i} = get_global_id(0);$

- 2: portfolio loss = 0.0

- 3: for j = 1 to numOfOblg do

- 4: Extract the  $S_j$ ,  $LGD_j$ ,  $C_j$ ,  $\beta_j$ ,  $\alpha_j$  from the input data.

- 5: Compute the composite risk factor:  $Y_j = \sum_{k=1}^{K} \alpha_{n,k} X_k$

- 6:  $ncdf = cdf((C_j Y_j * \beta_j)/(sqrt(1 \beta_j^2)))$

- 7:  $portfolioLoss + = S_j * LGD_j * (U_{i,j} < ncdf)$

- 8: end for

- 9: Result[i] = portfolioLoss

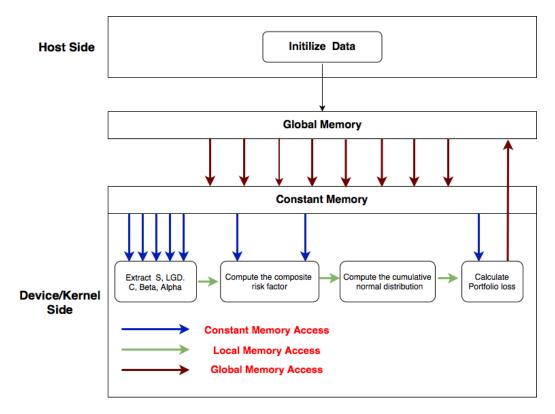

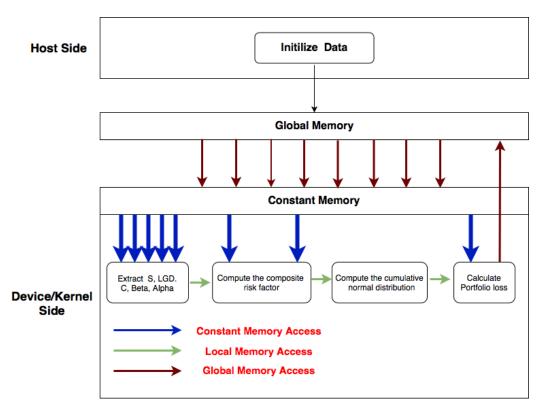

In the host side, after being initialised, the input data is then transferred to the FPGA side. Then the NDRange kernel is inserted into the command queue and starts to execute. Once all the threads running on the kernel finished their tasks, the kernel terminates and transfers the results back to the host side. Finally, the host side is responsible for the evaluation of the value at risk of this credit portfolio. An intuitive explanation of how the host and the FPGA collaborate is presented in Figure 3.3.

In the FPGA side, data transferred from the host side is first preloaded from global memory to constant memory. Then the kernel extracts data from the constant memory, uses the local memory to store and transform the runtime data, and write the results back to global memory in the end.

In our project, kernel computations are performed on constant memory mainly be-

cause it minimises the number of global memory access and reduces the memory latency through all work-groups and therefore improves the memory access efficiency. According to Zohouri et al.' s[14] study, due to its nature, constant caches are most appropriate for high-frequency data lookups that is constant across multiple invocations of a kernel. Besides, as suggested by the Intel Best Practice guide 2020[15], if there are any read-only data that is shared by all work-groups, then the data is better to be allocated in the constant memory. Our kernel precisely conforms to this case as according to the running process of the model we proposed in Figure 3.1, most of the input data, including S, LGD, C, etc., are all read-only data that shared by all work-groups.

To conclude, the basic implementation of the multi-factor Merton model in NDRange mode follows the procedure below, and its performance is as shown in Table 3.2.

Figure 3.3: NDRange Basic implementation

| Parameters/Devices   | FPGA                                             | CPU      |

|----------------------|--------------------------------------------------|----------|

| Time                 | 12651 ms                                         | 16936 ms |

|                      | Logic utilization = $20\%$                       |          |

|                      | ALUTs = 11% (91420/854400)                       |          |

| Resource utilisation | Dedicated logic registers = 10% (170876/1708800) | N/A      |

|                      | Memory blocks = $12\%$ ( $322/2713$ )            |          |

|                      | DSP blocks = 4% (60/1518)                        |          |

Table 3.2: Resource utilisation - NDRange Basic Implementation

### 3.2.2 Kernel vectorization implementation

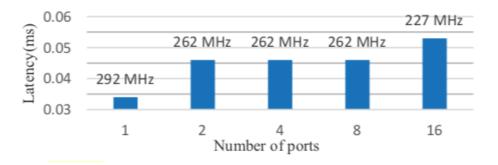

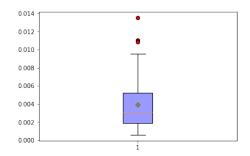

The following figure shows the results of an Intel FPGA SDK for OpenCL benchmark test conducted by Jia et al. in [16]. This diagram describes the relationship between cache frequency/latency and the number of access ports while using the same constant cache.

**Figure 3.4:** Constant cache latency and frequency with different number of ports (Obtained from "Tuning Stencil codes in OpenCL for FPGAs",2016)[16]

The latency of the constant cache accessed by a certain number of ports is described using the bars, and the numbers above each bar presents the corresponding frequency. It can be observed that the performance of the constant memory drops dramatically while the number of memory accessing requests is increased. Considering that in our implementation, the average number of ports access is 12 on average, the memory access speed of our NDRange implementation will be significantly affected. Therefore, we decided to use the technique of kernel vectorisation to alleviate this problem. Kernel vectorisation allows work items to be executed in a single instruction multiple data (SIMD) fashion, and therefore it can be used to reduce the number of ports accessing constant memory, and consequently, the access latency can be reduced. The principle of kernel vectorization is as shown in Figure 3.5. Intuitively, this technique splits the work among all the work-items within the work-group. For instance, if a kernel is executing a work-group that contains 16 work-items, then a kernel vectorization with a factor of 2 will reduce the total number of work-items to 8. As a result, the first work item will take over the work of the first and the second work-item, and so on.

Figure 3.5: The key idea of kernel vectorization

The Intel FPGA SDK for OpenCL Offline Compiler contains a built-in library that translates mathematical operations in the kernel, such as addition and subtraction, to its corresponding SIMD operation. Therefore in our work, kernel vectorization is easily done by including the *num\_simd\_work\_items* attribute in the kernel code. For example, in Figure 3.6 we apply a kernel vectorisation with a factor of four to the original kernel code that add two vectors. By setting the vectorization factor to 4, the compiler will be informed to vectorise the kernel four times to allow four work-items to be executed concurrently. That is, in each iteration, the kernel loads four elements from both arrays, instead of one element as before. The equivalent manually vectorisation implementation is shown in Figure 3.7. However, by doing

so, we need to adjust the NDRange size to a quarter of what it used to be, because each work-item takes over four times as much work after the manual optimisation is implemented. Therefore, in order to decrease the programming difficulty, we use OpenCL's build in kernel vectorization command directly (as shown in Figure 3.6).

| // Adding two vectors                                       |  |  |  |  |  |

|-------------------------------------------------------------|--|--|--|--|--|

| attribute ((num_simd_work_items(4)))                        |  |  |  |  |  |

| attribute((reqd_work_group_size(64,1,1)))                   |  |  |  |  |  |

| <pre>kernel void sum(global const float * restrict a,</pre> |  |  |  |  |  |

| <pre>global const float * restrict b,</pre>                 |  |  |  |  |  |

| global float * restrict output )                            |  |  |  |  |  |

| {                                                           |  |  |  |  |  |

| <pre>size_t gid = get_global_id(0);</pre>                   |  |  |  |  |  |

| <pre>output[gid] = a[gid] + b[gid];</pre>                   |  |  |  |  |  |

| }                                                           |  |  |  |  |  |

Figure 3.6: Kernel Vectorization using OpenCL SDK

```

// Adding two vectors

__kernel void sum(__global const float * restrict a,

___global const float * restrict b,

___global float * restrict output )

{

size_t gid = get_global_id(0);

output[gid * 4 + 0] = a[gid * 4 + 0] + b[gid * 4 + 0];

output[gid * 4 + 1] = a[gid * 4 + 1] + b[gid * 4 + 1];

output[gid * 4 + 2] = a[gid * 4 + 2] + b[gid * 4 + 2];

output[gid * 4 + 3] = a[gid * 4 + 3] + b[gid * 4 + 3];

}

```

Figure 3.7: Kernel Vectorization manually

To conclude, by using the Kernel Vectorization technique, the kernel can access multiple times as much data as before. This is indicated by the broad arrows in Figure 3.8.

Figure 3.8: NDRange mode - Kernel Vectorization implementation

To execute multiple work-items concurrently, the compiler increase the hardware utilization to do so. In our Kernel Vectorization implementation, we have utilised a vectorisation factor of 16, and it can be seen that the resource utilisation has increased as shown in Table 3.3 when compared to the basic implementation's resource utilisation presented in Table 3.2. However, we could also observe that compare to the basic implementation of NDRange modes, vectorise the kernel helps to improve the performance by up to 200.9%. This indicates that our kernel vectorisation strategy is effective.

Table 3.3: Resource utilization - Kernel Vectorization Implementation

| Parameters/Devices   | FPGA                                             | CPU      |

|----------------------|--------------------------------------------------|----------|

| Time                 | 6295 ms                                          | 16936 ms |

|                      | Logic utilization = $62\%$                       |          |

|                      | ALUTs = 39% (331507/854400)                      |          |

| Resource utilization | Dedicated logic registers = 26% (444288/1708800) | N/A      |

|                      | Memory blocks = 44% (1191/2713)                  |          |

|                      | DSP blocks = 45% (680/1518)                      |          |

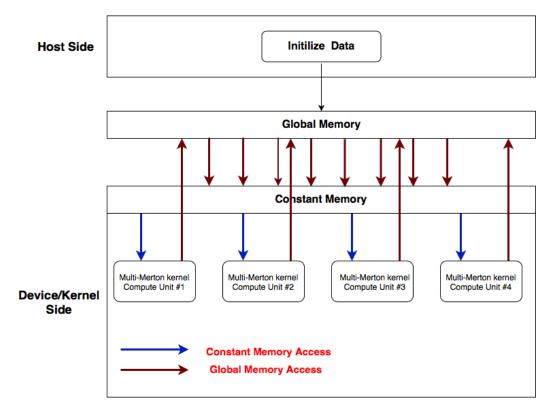

### 3.2.3 Multiple compute units implementation

This section discusses the second optimisation technique under the NDRange mode - increase the number of compute units. In the NDRange mode, work-groups run on multiple compute units. Each compute unit is implemented as a unique pipeline, and can execute multiple work-groups at the same time. By default, work-groups are dispatched automatically by the FPGA hardware scheduler to available compute units. A compute unit is able to be assigned work-groups as long as it does not exceeds its maximum capacity. If there are two compute units available, then each compute unit is responsible for executing half of the work-groups. In case that each work-group takes the same amount of time to complete its tasks, then in theory, the total running time can be cut in half if there are enough hardware resources.

For example, if we decide to increase the number of compute units to 4, then the compiler will create four unique compute units as showed in Figure 3.9;

Figure 3.9: NDRange - Multiple Compute Units implementation

Therefore, we also tried to optimize our FPGA implementation by increasing the number of compute units per kernel to 12. In our work, this is done by specifying the number of compute units that the OpenCL FPGA compiler is expected to create using

the *num\_compute\_units* attribute, as shown below. The corresponding performance is presented in Table 3.4.

Figure 3.10: Pseudo code for multiple compute units implementation

However, through experiment we found that increase the number of compute units to improve the performance of our FPGA implementation leads to the following two problems.

- To increase the number of compute units, the compiler adds the necessary recourses to do so. It can be seen that compared with the basic implementation, the improvement of resource usage in Table 3.4 is similar to that of the kernel vectorization implementation in Table 3.3.

- A higher throughput can be achieved by increasing the number of compute units. However, as shown in figure 3.9, it do so at the expense of increasing memory bandwidth(4 loads and 4 store, instead of 1 load and 1 store of the kernel vectorization implementation).

Because of the above two reasons, from Table 3.4 we can find that when use 12 compute units to optimize the implementation, the kernel running speed was only improved a little bit compared to the basic NDRange implementation, and its acceleration effect is far from that of kernel vectorization.

| Parameters/Devices   | FPGA                                             | CPU      |

|----------------------|--------------------------------------------------|----------|

| Time                 | 11980 ms                                         | 16900 ms |

|                      | Logic utilization = $73\%$                       |          |

|                      | ALUTs = 43% (364828/854400)                      |          |

| Resource utilization | Dedicated logic registers = 33% (562196/1708800) | N/A      |

|                      | Memory blocks = $63\%$ (1710/2713)               |          |

|                      | DSP blocks = 47% (713/1518)                      |          |

Table 3.4: Resource utilization - 12 Compute Units Implementation

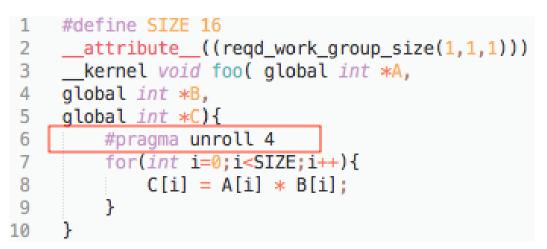

## 3.2.4 Loop unrolling implementation

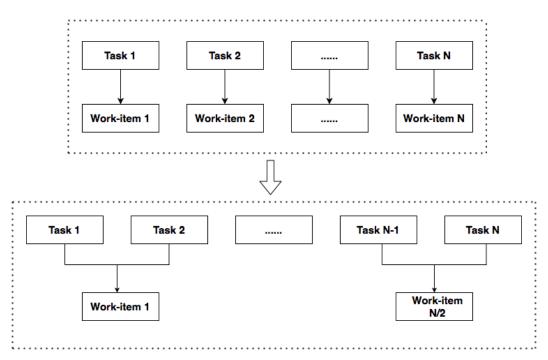

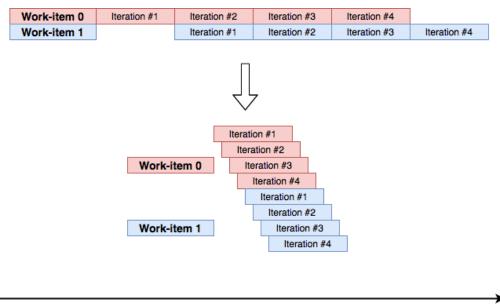

Since there are a large number of loops in our kernel code, we also tried the loop unrolling strategy to improve the performance of our loop Iterations. Loop unrolling is a loop transformation technique that helps to improve the running speed of a program. It works by replicating the body of a loop multiple times so that the number of iterations of a loop can be reduced. Intuitively, the aim is to flatten the loop structure and execute all iterations of the loop in one feed-forward path.

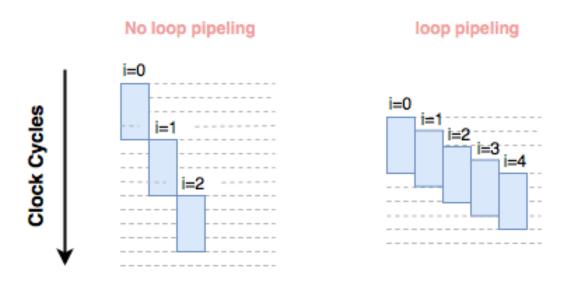

Loop unrolling optimizes the loop's performance in two aspects. First of all, it remove or reduce iterations. This increases the program's speed by eliminating the consumption of loop control instructions. Secondly, there exists a lot of loops that are not pipelined in the NDRange kernel. If the loops are not pipelined, then the optimal case will be that it can be completely unrolled so that the loop is removed. By doing so, for the offline compiler, the loop iterations is equivalent to be fully pipelined as there is no loop anymore. This can be explained more intuitively using the figure below, where the above one describes the running process without loop unrolling, while the bottom one shows the running process with fully loop unrolled.

**Clock Cycles**

Figure 3.11: loop rolling vs loop unrolling

From the figure we can observe that, without loop unrolling, loops in a FPGA kernel is not well pipelined. Whereas unrolling the loop enables the operations inside a work item to be pipelined, this make the entire pipeline wider so that more tasks can be executed in parallel.

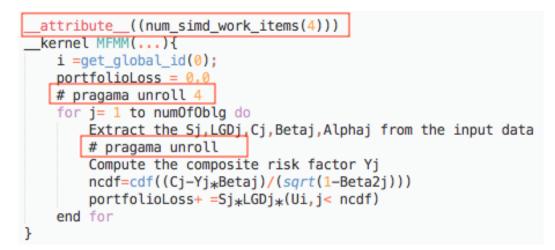

In our work, loop unrolling is done by adding a  $\# pragma \ unroll$  attribute to the main loop, as shown in the code example below.

Figure 3.12: OpenCL SDK loop unroll 4 times

We implemented two different loop unrolling implementations that used two differ-

ent combinations of the unrolling factor. Algorithm 3 shows our first loop unrolling implementation. The outer loop was unrolled with 4 times and the inner loop was fully unrolled. By doing so, from Table 3.5, it can be found that the algorithm has got a speed up of factor 8 at the expense of increased hardware utilization.

Algorithm 4 shows our second loop unrolling implementation, where the loop unroll factor of the outer loop was changed to 8. From Table 3.6, it can be observed that it consumes about 1.5 times the hardware utilization of the basic implementation to give us about the same improvement in performance which is very ineffective. Therefore, in our optimised implementation, the first loop unrolling factor combination is used.

#### Algorithm 3 multi-factor Merton model - Loop unrolling implementation 1

```

1: \mathbf{i} = get_global_id(0);

```

2: portfolioLoss = 0.0

```

3: # pragama unroll 4

```

- 4: for j = 1 to numOfOblg do

- 5: Extract the  $S_j$ ,  $LGD_j$ ,  $C_j$ ,  $\beta_j$ ,  $\alpha_j$  from the input data.

- 6: # pragama unroll

- 7: Compute the composite risk factor:  $Y_j = \sum_{k=1}^{K} \alpha_{n,k} X_k$

- 8:  $ncdf = cdf((C_j Y_j * \beta_j)/(sqrt(1 \beta_i^2)))$

- 9:  $portfolioLoss + = S_j * LGD_j * (U_{i,j} < ncdf)$

- 10: end for

- 11: Result[i] = portfolioLoss

#### Table 3.5: Resource utilization - Loop Unrolling Implementation 1

| Parameters/Devices   | FPGA                                             | CPU      |

|----------------------|--------------------------------------------------|----------|

| Time                 | 2445 ms                                          | 16936 ms |

|                      | Logic utilization = 35%                          |          |

|                      | ALUTs = 19% (162324/854400)                      |          |

| Resource utilization | Dedicated logic registers = 18% (307583/1708800) | N/A      |

|                      | Memory blocks = $30\%$ (811/2713)                |          |

|                      | DSP blocks = 14% (212/1518)                      |          |

Algorithm 4 Multi Factor Merton Model - Loop unrolling implementation 2

- 1:  $\mathbf{i} = get_global_id(0);$

- 2: portfolioLoss = 0.0

- 3: # pragama unroll 8

- 4: for j = 1 to numOfOblg do

- 5: Extract the  $S_j$ ,  $LGD_j$ ,  $C_j$ ,  $\beta_j$ ,  $\alpha_j$  from the input data.

- 6: # pragama unroll

- 7: Compute the composite risk factor:  $Y_j = \sum_{k=1}^{K} \alpha_{n,k} X_k$

- 8:  $ncdf = cdf((C_j Y_j * \beta_j)/(sqrt(1 \beta_j^2)))$

- 9:  $portfolioLoss + = S_j * LGD_j * (U_{i,j} < ncdf)$

- 10: end for

- 11: Result[i] = portfolioLoss

#### Table 3.6: Resource utilization - Loop Unrolling implementation 2

| Parameters/Devices FPGA |                                                  | CPU      |

|-------------------------|--------------------------------------------------|----------|

| Time 2510 ms            |                                                  | 16936 ms |

| Resource utilization    | Logic utilization = $51\%$                       |          |

|                         | ALUTs = 28% (237523/854400)                      |          |

|                         | Dedicated logic registers = 25% (427200/1708800) | N/A      |

|                         | Memory blocks = $46\%$ (1245/2713)               |          |

|                         | DSP blocks = 27% (406/1518)                      |          |

### 3.3 Single work-item

The single work-item kernels is equivalent to NDRange kernels with only one workgroup and each work-group contains only one work-item. Ordinary C/C++ programs is based on sequential models, which execute each element sequentialy, with no overlap between the execution of the elements, as described in Figure 3.13(left). Whereas in single work-item kernels, the compiler will infer pipelined execution across loop iterations and builds all the loops to iterate sequentially through the pipeline. That is, a work-item is inserted into the pipeline in each clock cycle so that multiple work-items can be executed in parallel to maximize the utilization of hardware resources.

Figure 3.13: sequential mode vs loop pipeling

### 3.3.1 Single work-item basic implementation

The basic implementation of single work-item kernel is very similar to that of the original C++ implementation, as shown in the pseudo code below.

Algorithm 5 Single work-item mode - Basic implementation 1: for i = 1 to numOfScenario do portfolioLoss = 0.02: for j = 1 to numOfOblg do 3: Extract the  $S_j$ ,  $LGD_j$ ,  $C_j$ ,  $\beta_j$ ,  $\alpha_j$  from the input data. 4: for k = 1 to numOfFactor do 5:  $Y_i + = X(i, j) * Alpha(j, k)$ 6: end for 7:  $ncdf = cdf((C_i - Y_i * \beta_i) / (sqrt(1 - \beta_i^2)))$ 8:  $portfolioLoss + = S_j * LGD_j * (U_{i,j} < ncdf)$ 9: end for 10: Result[i] = portfolioLoss11: 12: end for

The basic implementation above has three sets of nested loops. The outer loop is responsible for doing Monte-Carlo simulations, the middle loop calculates each obigor's loss value, and the inner loop is responsible for calculating the composite risk factor of each obligor based on the systematic factors x and the dependence

variable  $\alpha$ .

Similar to our NDRange mode implementation, the basic implementation of single work-item kernel will also first transferred the data from the global memory to the constant memory. This is because the main difference between the single work-item kernel and the NDRange kernel is the different division of work-groups and work-items. As the data used by different work-groups in our model is identical, theoretically, single work-item kernels can adopt the same memory accessing method as NDRange Kernel models. By doing so, the memory access efficiency can be improved without affecting the accuracy of the running results.

As we said before, the single work-item mode mainly speed up the kernel through pipeline parallelization. Therefore, the OpenCL FPGA compiler always generates an optimization report on how well the single work-item kernel is pipelined, as shown in Figure 3.14.

|                                                                                                                                                                                                                                                          |                                                                                                                  |                                             |        |           | <b>2</b> S        | Show fully unrolled loops   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|---------------------------------------------|--------|-----------|-------------------|-----------------------------|

|                                                                                                                                                                                                                                                          |                                                                                                                  | Pipelined                                   | Ш      | Speculate | ed iterations     | Details                     |

| ernel: simpleMultiply (covariance.cl:41)                                                                                                                                                                                                                 |                                                                                                                  |                                             |        |           |                   | Single work-item execut     |

| simpleMultiply.B1 (covariance.cl:63)                                                                                                                                                                                                                     |                                                                                                                  | Yes                                         | >=1    | 0         |                   |                             |

| simpleMultiply.B4 (covariance.cl:66)                                                                                                                                                                                                                     |                                                                                                                  | Yes                                         | >=1    | 0         |                   |                             |

| simpleMultiply.B6 (covariance.cl:75)                                                                                                                                                                                                                     |                                                                                                                  | Yes                                         | ~1     | 0         |                   |                             |

|                                                                                                                                                                                                                                                          |                                                                                                                  |                                             |        |           |                   |                             |

| may Il Dapart                                                                                                                                                                                                                                            |                                                                                                                  |                                             |        |           |                   |                             |

| max ii Report                                                                                                                                                                                                                                            |                                                                                                                  |                                             |        |           |                   |                             |

| max ii keport                                                                                                                                                                                                                                            | Target II                                                                                                        | Scheduled                                   | d Fmax | Block II  | Latency           | Max Interleaving Iterations |

|                                                                                                                                                                                                                                                          |                                                                                                                  |                                             | d Fmax | Block II  | Latency           | Max Interleaving Iterations |

|                                                                                                                                                                                                                                                          |                                                                                                                  |                                             | d Fmax | Block II  | Latency<br>2      | Max Interleaving Iterations |

| rnel: simpleMultiply ( Target Fmax : Not speci                                                                                                                                                                                                           | fied MHz ) ( covariance.                                                                                         | cl:41 )                                     | d Fmax |           |                   |                             |

| rnel: simpleMultiply (Target Fmax : Not speci<br>Block: simpleMultiply.B0                                                                                                                                                                                | fied MHz ) ( covariance.<br>Not specified                                                                        | <b>cl:41 )</b><br>240.0                     | 1 Fmax | 1         | 2                 | 1                           |

| rnel: simpleMultiply ( Target Fmax : Not speci<br>Block: simpleMultiply.B0<br>Block: simpleMultiply.B2                                                                                                                                                   | fied MHz ) ( covariance.<br>Not specified                                                                        | <b>cl:41 )</b><br>240.0                     | d Fmax | 1         | 2                 | 1                           |

| rnel: simpleMultiply (Target Fmax : Not speci<br>Block: simpleMultiply.B0<br>Block: simpleMultiply.B2<br>Loop: simpleMultiply.B1 (covariance.cl:63)                                                                                                      | fied MHz ) ( covariance.<br>Not specified<br>Not specified<br>Not specified                                      | <b>cl:41 )</b><br>240.0<br>240.0            | d Fmax | 1         | 2                 | 1                           |

| ernel: simpleMultiply ( Target Fmax : Not speci<br>Block: simpleMultiply.B0<br>Block: simpleMultiply.B2<br>Loop: simpleMultiply.B1 (covariance.cl:63)<br>Block: simpleMultiply.B1                                                                        | fied MHz ) ( covariance.<br>Not specified<br>Not specified<br>Not specified                                      | <b>cl:41 )</b><br>240.0<br>240.0            | d Fmax | 1         | 2                 | 1                           |

| ernel: simpleMultiply (Target Fmax : Not speci<br>Block: simpleMultiply.B0<br>Block: simpleMultiply.B2<br>Loop: simpleMultiply.B1 (covariance.ct:63)<br>Block: simpleMultiply.B1<br>Loop: simpleMultiply.B4 (covariance.ct:                              | fied MHz ) ( covariance.<br>Not specified<br>Not specified<br>Not specified<br>56)<br>Not specified              | ct:41 )<br>240.0<br>240.0<br>240.0          | d Fmax | 1         | 2<br>0<br>7       | 1                           |

| ernel: simpleMultiply ( Target Fmax : Not speci<br>Block: simpleMultiply.B0<br>Block: simpleMultiply.B2<br>Loop: simpleMultiply.B1 (covariance.cl:63)<br>Block: simpleMultiply.B1<br>Loop: simpleMultiply.B4 (covariance.cl:<br>Block: simpleMultiply.B4 | fied MHz ) ( covariance.<br>Not specified<br>Not specified<br>Not specified<br>56)<br>Not specified              | ct:41 )<br>240.0<br>240.0<br>240.0          | d Fmax | 1         | 2<br>0<br>7       | 1                           |

| Block: simpleMultiply.B1 (covariance.cl:63)<br>Block: simpleMultiply.B1<br>Loop: simpleMultiply.B1<br>Loop: simpleMultiply.B4 (covariance.cl:<br>Block: simpleMultiply.B4<br>Loop: simpleMultiply.B6 (covariance.cl:                                     | fied MHz ) ( covariance.<br>Not specified<br>Not specified<br>Not specified<br>S66)<br>Not specified<br>e.ct:75) | ct:41 )<br>240.0<br>240.0<br>240.0<br>240.0 | d Fmax | 1<br>1    | 2<br>0<br>7<br>15 | 1                           |

Figure 3.14: Single work-item kernel basic implementation performance report

The initiation interval (II) in the report refers to the launch frequency of a loop's new iteration. It describes the number of hardware clock cycles the pipeline must wait for before continuing with the next loop iteration. By referring the report, we can observe that the compiler successfully infers pipelined execution for the inner most loop and it shows an optimal loop performance as it has an II value of 1, which indicates that iterations were launched every cycle. The outer two loops were also pipelined successfully, but their iterations were launched every two cycles because they have a inner loop inside them. Overall, the optimization report shows that the kernel was well pipelined. From Table 3.7, we see that without any optimization methods, the basic implementation produced a 2x improvement in running speed compared to that of the C++ basic implementation on the CPU.

| Parameters/Devices   | Parameters/Devices FPGA                          |          |

|----------------------|--------------------------------------------------|----------|

| Time                 | 7392 ms                                          | 16936 ms |

|                      | Logic utilization = $21\%$                       |          |

| Resource utilization | ALUTs = 11% (93976/854400)                       |          |

|                      | Dedicated logic registers = 10% (170879/1708800) | N/A      |

|                      | Memory blocks = $11\%$ (279/2713)                |          |

|                      | DSP blocks = 4% (60/1518)                        |          |

Table 3.7: Resource utilization - Single work-item basic implementation

### 3.3.2 Loop unrolling implementation

Loop unrolling reduces the number of iterations of a loop at the expense of increasing hardware utilization. Since it is able to increase the throughput of the kernel and widen the pipeline, loop unrolling usually brings a speed up effect. Therefore, we have also tried to use loop unrolling to improve the performance of the single work-item kernel. In this implementation, as we can see from the code in Algorithm 6, we have unrolled the outer two loops with a factor of 4 and fully unrolled the inner most loop, like in our optimal loop unrolling implementation under NDRange mode.

#### Algorithm 6 Single work-item kernel loop unrolling implementation

```

1: #pragma unroll 4

```

- 2: for i = 1 to numOfScenario do

- 3: portfolioLoss = 0.0

- 4: #pragma unroll 4

- 5: **for** j = 1 to numOfOblg **do**

- 6: Extract the  $S_i$ ,  $LGD_i$ ,  $C_i$ ,  $\beta_i$ ,  $\alpha_i$  from the input data.

- 7: #pragma unroll

- 8: **for** k = 1 to numOfFactor **do**

```

9: Y_j + = X(i, j) * Alpha(j, k)

```

10: **end for**

```

11: ncdf = cdf((C_j - Y_j * \beta_j)/(sqrt(1 - \beta_j^2)))

```

12:  $portfolioLoss + = S_j * LGD_j * (U_{i,j} < ncdf)$

```

13: end for

```

```

14: Result[i] = portfolioLoss

```

```

15: end for

```

From the optimization report in Figure 3.15, we can see that after using loop unrolling, both three loops are well pipelined, the initiation intervals are also within a reasonable range. This indicates that the use of the loop unrolling technique does not affect single work-item kernel's parallel pipelining structure. From Table 3.8, we can see that the performance has increased significantly benefits from the use of loop unrolling.

| Loops Analysis Show fully unrolled loops    |                           |                |       |                |              |                   |      |

|---------------------------------------------|---------------------------|----------------|-------|----------------|--------------|-------------------|------|

|                                             |                           | Pipelined      | Ш     | Speculated ite | rations      | Details           |      |

| Kernel: simpleMultiply (covariance.cl:41)   |                           |                |       |                |              | Single work-item  | exec |

| 4X Partially unrolled simpleMultiply.B1 (   | ovariance.cl:63)          | Yes            | >=1   | 0              |              |                   |      |

| 4X Partially unrolled simpleMultiply.       | B3 (covariance.cl:66)     | Yes            | ~1    | 0              |              |                   |      |

| Fully unrolled loop (covariance.c           | 1:75)                     | n/a            | n/a   | n/a            |              | Unrolled by #prag | gma  |

| 4X Partially unrolled simpleMultiply.       | B4 (covariance.cl:66)     | Yes            | ~1    | 0              |              |                   |      |

| 4X Partially unrolled simpleMultiply.       | B5 (covariance.cl:66)     | Yes            | ~1    | 0              |              |                   |      |

| 4X Partially unrolled simpleMultiply.       | B6 (covariance.cl:66)     | Yes            | ~1    | 0              |              |                   |      |

| Fmax II Report                              |                           |                |       |                |              |                   |      |

|                                             | Target II                 | Scheduled Fmax | Block | II Latency     | Max Interlea | aving Iterations  |      |

| ernel: simpleMultiply ( Target Fmax : Not s | pecified MHz ) ( covarian | ace.cl:41)     |       |                |              |                   |      |

| Block: simpleMultiply.B0                    | Not specified             | 240.0          | 1     | 2              | 1            |                   |      |

| Block: simpleMultiply.B2                    | Not specified             | 240.0          | 1     | 0              | 1            |                   |      |

| Loop: simpleMultiply.B1 (covariance.cl:     | 63)                       |                |       |                |              |                   |      |

| Block: simpleMultiply.B1                    | Not specified             | 240.0          | 1     | 17             | 1            |                   |      |

| Loop: simpleMultiply.B3 (covariand          | :e.cl:66)                 |                |       |                |              |                   |      |

| Block: simpleMultiply.B3                    | Not specified             | 114.8          | 1     | 222            | 1            |                   |      |

| Loop: simpleMultiply.B4 (covariand          | :e.cl:66)                 |                |       |                |              |                   |      |

| Block: simpleMultiply.B4                    | Not specified             | 114.8          | 1     | 216            | 1            |                   |      |

| Loop: simpleMultiply.B5 (covariand          | e.cl:66)                  |                |       |                |              |                   |      |

| Block: simpleMultiply.B5                    | Not specified             | 114.8          | 1     | 216            | 1            |                   |      |

| Loop: simpleMultiply.B6 (covariand          | :e.cl:66)                 |                |       |                |              |                   |      |

| Block: simpleMultiply.B6                    | Not specified             | 114.8          | 1     | 216            | 1            |                   |      |

| Block: simpleMultiply.B7                    | Not specified             | 240.0          | 1     | 12             | 1            |                   |      |

| Block: simpleMultiply.B8                    | Not specified             | 240.0          | 1     | 12             | 1            |                   |      |

| Riock: cimpleMultiply R0                    | Not specified             | 240.0          | 1     | 12             | 1            |                   |      |

Figure 3.15: Single work-item loop unrolling performance report

Table 3.8: Resource utilization - Single work-item loop unrolling implementation

| Parameters/Devices   | ES FPGA                                          |          |

|----------------------|--------------------------------------------------|----------|

| Time 1592 ms         |                                                  | 16936 ms |

|                      | Logic utilization $= 85\%$                       |          |

| Resource utilization | ALUTs = 41% (347740/854400)                      |          |

|                      | Dedicated logic registers = 31% (529714/1708800) | N/A      |

|                      | Memory blocks = 71% (1902/2713)                  |          |

|                      | DSP blocks = 42% (637/1518)                      |          |

## 3.4 Fixed point vs Floating point

The input of the kernel that running the multi-factor Merton model consists of floating point numbers, which results in a huge consumption of hardware resources. However, in Intel FPGA SDK for OpenCL, fixed-point operations typically require less hardware resources than the equivalent floating-point operation. This indicates that we could save more hardware resources by using fixed-point data representations. Therefore, we have also tried to use fixed-point representation to improve the performance of our implementation

The fixed-point representation's bit length of the fractional parts and integer parts can be determined according to the sample data intensity range and a minimum fractional accuracy. The intensity range of the multi-factor Merton model's input data is quite straightforward to be determined. According to the requirements of the model, the input data of the model can generally be stored in 8-bit variables. However, the simulation procedure requires the input data to be summed, multiplied and scaled. Therefore, in order to avoid arithmetic overflow, it will be better to use a longer bit lengths. In order to figure out the most appropriate bit length of the fixed-point representation, an analysis of the input and intermediate data value intensities was performed. As a result, it was finally decided to adopt 17-bits fixed-point data representation: 4 bits for integer part and 13 bits for fractional part.

Since the Intel FPGA SDK for OpenCL does not support fixed-point representation, the conversion is done manually on the host side using the following equations:

$$fixed\_point\_input = floating\_point\_input * (1 << fractional\_bits)$$

(3.1)

$$floating\_point\_output = fixed\_point\_output/(1 << fractional\_bits)$$

(3.2)

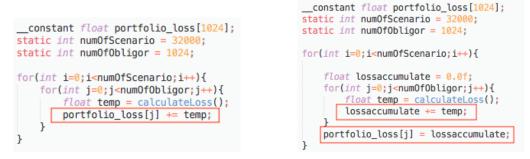

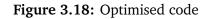

The two tables below shows the influence of using fixed point on our optimised FPGA implementation (which is our best-performing implementations, this will be discussed in Section3.5). It can be observed that, as we expected, using fixed point number saves a lot of hardware resources, especially the resources of digital signal processing (DSP) blocks. Besides, it can be seen that compared to the floating point implementation, using fixed-point further increase the speed up effect for 15%.

This indicates that using fixed-point data is a efficient way to improve the running speed of our FPGA implementation.

| Parameters/Devices   | FPGA                                             | CPU      |

|----------------------|--------------------------------------------------|----------|

| Time                 | 769 ms                                           | 16936 ms |

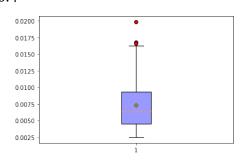

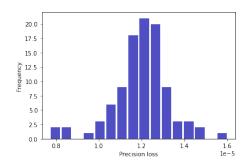

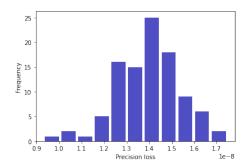

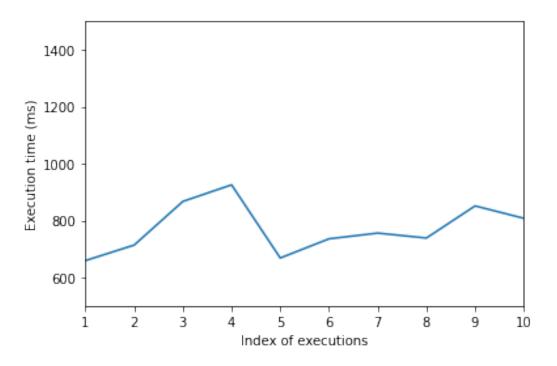

|                      | Logic utilization $= 65\%$                       |          |